132 reads

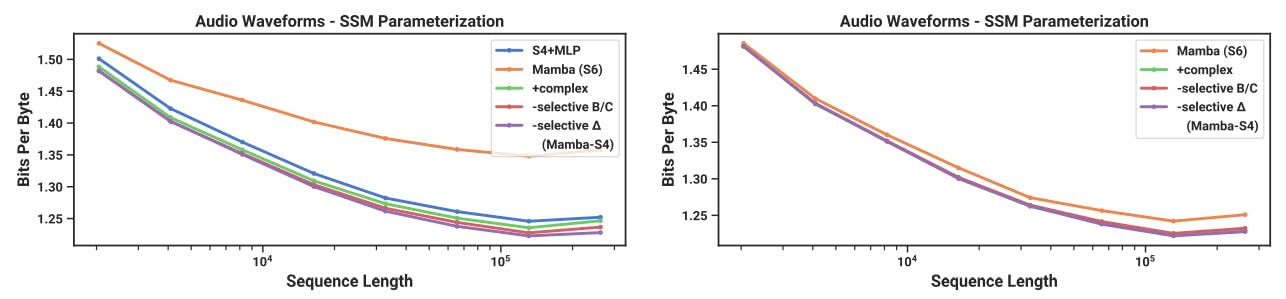

Hardware-Aware Algorithm for Selective State Space Models

by

December 18th, 2024

We cover the most cutting edge academic research and expert blog posts on serialization. Also big fans of the Serial pod

Story's Credibility

About Author

We cover the most cutting edge academic research and expert blog posts on serialization. Also big fans of the Serial pod